- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX11202BEUB+T (Maxim Integrated Products)IC ADC 24BIT SRL 13.75SPS 10UMAX

3

Maxim Integrated

24-Bit, Single-Channel, Ultra-Low-Power, Delta

Sigma ADC with 2-Wire Serial Interface

MAX11202

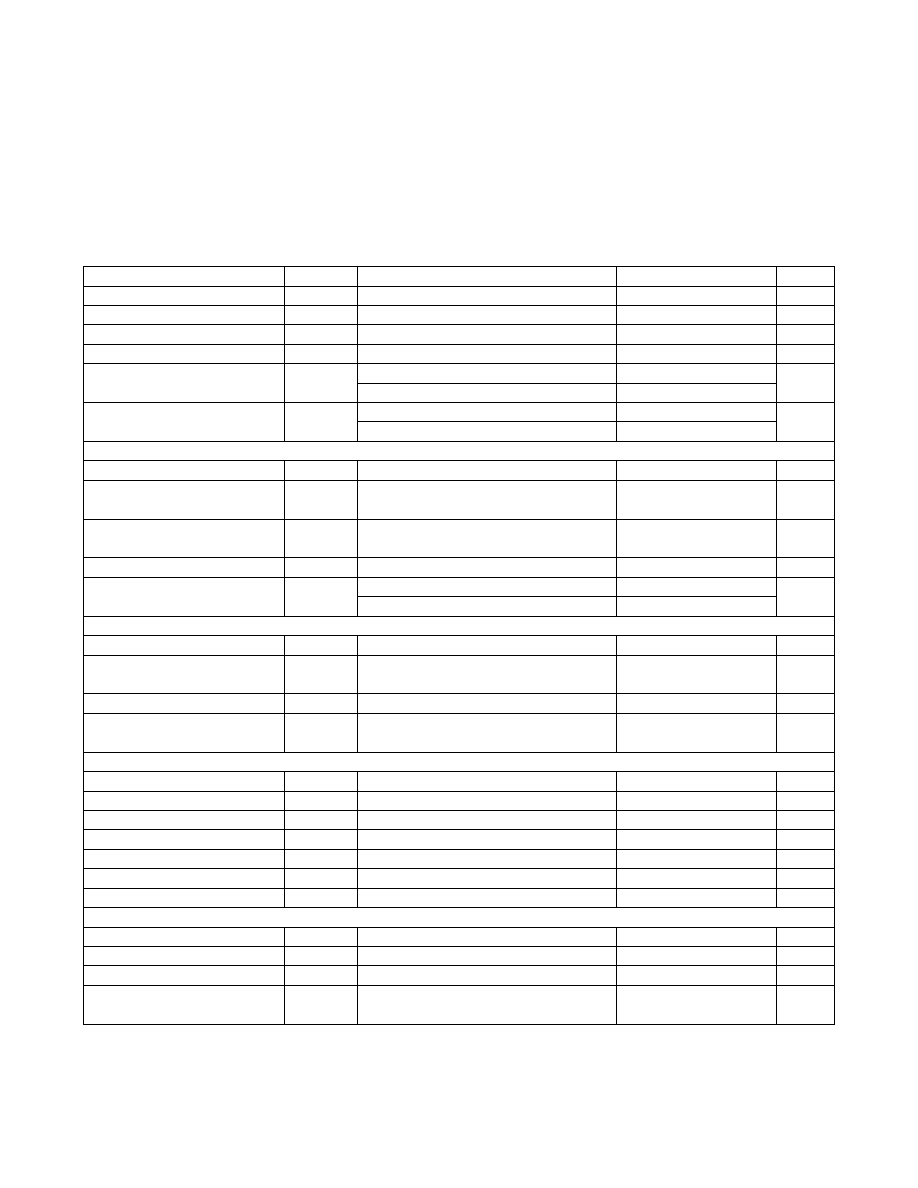

ELECTRICAL CHARACTERISTICS (continued)

(VAVDD = +3.6V, VDVDD = +1.8V, VREFP - VREFN = VAVDD; internal clock, TA = TMIN to TMAX, unless otherwise noted. Typical values

are at TA = +25NC under normal conditions, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

AIN Input Capacitance

10

pF

REF Input Capacitance

15

pF

AIN Voltage Range

AINP - AINN

-VREF

+VREF

V

REF Voltage Range

VAVDD

V

Input Sampling Rate

fS

MAX11202A

246

kHz

MAX11202B

225

REF Sampling Rate

MAX11202A

246

kHz

MAX11202B

225

LOGIC INPUTS (SCLK, CLK)

Input Current

Input leakage current

Q

1

F

A

Input Low Voltage

VIL

0.3 x

VDVDD

V

Input High Voltage

VIH

0.7 x

VDVDD

V

Input Hysteresis

VHYS

200

mV

External Clock

MAX11202A

2.4576

MHz

MAX11202B

2.2528

LOGIC OUTPUT (RDY/DOUT)

Output Low Level

VOL

IOL = 1mA; also tested for VDVDD = 3.6V

0.4

V

Output High Level

VOH

IOH = 1mA; also tested for VDVDD = 3.6V

0.9 x

VDVDD

V

Floating State Leakage Current

Output leakage current

Q

10

F

A

Floating State Output

Capacitance

9

pF

POWER REQUIREMENTS

Analog Supply Voltage

AVDD

2.7

3.6

V

Digital Supply Voltage

DVDD

1.7

3.6

V

Total Operating Current

AVDD + DVDD

230

300

F

A

DVDD Operating Current

45

60

F

A

AVDD Operating Current

185

245

F

A

AVDD Sleep Current

0.4

2

F

A

DVDD Sleep Current

0.35

2

F

A

2-WIRE SERIAL-INTERFACE TIMING CHARACTERISTICS

SCLK Frequency

fSCLK

5

MHz

SCLK Pulse Width Low

t1

60/40 duty cycle, 5MHz clock

80

ns

SCLK Pulse Width High

t2

40/60 duty cycle, 5MHz clock

80

ns

SCLK Rising Edge to Data Valid

Transition Time

t3

40

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX11210EEE+T

ADC 24BIT 4WIRE SPI 16-QSOP

MAX11212BEUB+T

IC ADC 18BIT SRL 13.75SPS 10UMAX

MAX1135BCAP+

IC ADC 16BIT 150KSPS 20-SSOP

MAX1138LEEE+T

IC ADC 10BIT SERIAL 16-QSOP

MAX1159AEUI+

IC ADC 14BIT 135KSPS 28-TSSOP

MAX11602EEE+

IC ADC SERIAL 8BIT 8CH 16-QSOP

MAX11610EEE+T

IC ADC SERIAL 10BIT 12CH 16-QSOP

MAX11616EEE+T

IC ADC SERIAL 12BIT 12CH 16-QSOP

相关代理商/技术参数

MAX11202EUB+

功能描述:模数转换器 - ADC 24 Bit Sigma Delta ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11202EUB+T

功能描述:模数转换器 - ADC 24 Bit Sigma Delta ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11203

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:16-Bit, Single-Channel, Ultra-Low-Power, Delta-Sigma ADCs with Programmable Gain and GPIO

MAX11203EEE+

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11203EEE+T

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11205

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:16-Bit, Single-Channel, Ultra-Low Power, Delta-Sigma ADC with 2-Wire Serial Interface

MAX11205AEUB+

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11205AEUB+T

功能描述:模数转换器 - ADC 16-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32